2月4日消息,国产香山团队于近日正式将其高性能内存控制器IP开源,该IP代号为“玉泉”,其中DDR4控制器IP的代号是“白杨”,这对香山处理器项目以及其内存子系统研究而言,具有里程碑式的重要意义。

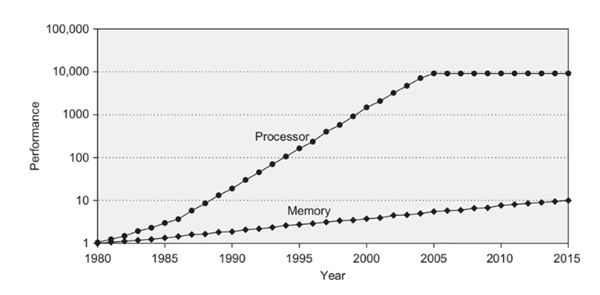

官方表示,随着CPU计算能力持续飞速提升,内存子系统的性能瓶颈日益凸显。

CPU频率的提升并没有让系统整体性能同步提高,这是因为内存性能的发展速度远远跟不上处理器,这种木桶效应使得访存延迟成了限制整个系统性能的关键瓶颈。

在大数据与人工智能时代,这一矛盾尤为突出。

为了缓解内存墙问题,研究者们提出了诸多解决方案,其中高性能内存控制器是关键技术之一,它可以有效提高内存访问效率、减少延迟、提升带宽利用率,进而缓解内存墙对系统性能的限制。

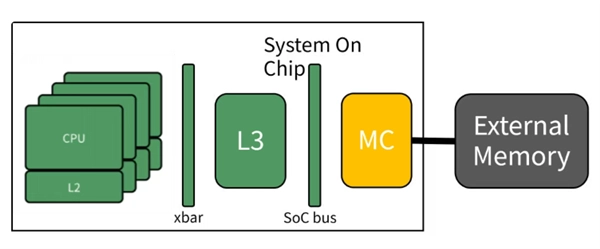

与此同时,香山开源处理器核已快速演进至第三代(昆明湖),其内存访问路径持续升级,各级缓存(L1-L2-L3)的架构与性能也在不断优化。

然而,作为连接处理器与内存的关键部件,内存控制器在开源生态中仍处于相对简单(dumb)的状态。

它的性能优化情况直接关系到处理器核性能上限的发挥,然而目前既缺乏能与处理器架构开展联合优化的创新方案,国内外已有的开源项目也无法满足对高性能内存控制器IP的需求。

目前阶段,内存控制器IP的主流市场由少数几家供应商所垄断,其授权费用极为高昂,像一个DDR5 IP的单项目授权费用就可能达到80万到150万美元,并且这些IP存在大量可配置参数,使得开发与调试的门槛较高。

Synopsys:提供DDR4/DDR5/LPDDR5/HBM等IP授权

Cadence:提供LPDDR6/5X/HBM4等IP授权

Alphawave:提供HBM3/UCIe/CXL等IP授权

Rambus:提供DDR3/DDR4/GDDR6/HBM3等IP授权

ARM/Intel/Qualcomm:通常将内存控制器作为芯片组的一部分提供,需购买其芯片获取

现有的开源内存控制器项目,大多面向特定或轻量级应用场景,在性能、功能完备性和流片支持上存在明显不足。

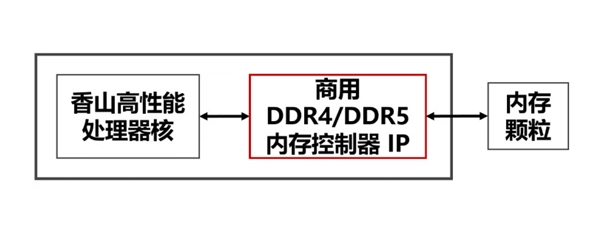

现在,香山采用的流片方案是使用商用DDR4/DDR5内存控制器IP,但也存在一些问题:

-成本高昂:先进工艺节点的DDR5 IP授权费用极其昂贵。

-优化困难:难以结合香山处理器核独特的访存特征进行针对性优化。商用IP动辄数百个的可配置参数,也缺乏科学的设计空间探索方法来进行有效调优。

针对这些挑战,白杨IP在设计之初就设定了明确目标:填补从一般性开源MC IP到可供开源生态自主演进的高性能MC IP之间的技术鸿沟。

其设计方案借助对问题的分解、融合与提炼,能够把七个需要解决的难点转化为四项研究问题,具体包括:MC具备参数化与可配置能力,能够实现模块化分解和复用,支持动态刷新、动态调度、缓存、预取等高级功能,以及兼容DFIx、AXI4等总线协议。

白杨”IP采用模块化、可配置的架构设计,除了实现内存控制器的基本功能外,还集成了多项高级特性:

软件可配置:通过APB接口,软件可以访问和配置内存控制器内部的寄存器,从而灵活支持各种DDR配置。

时序与调度解耦:把DDR时序逻辑和事务调度器(Scheduler)分离开来。这样的设计能让调度器逻辑在不同的DDR配置里重复使用,从而增强设计的灵活性和可维护性。

高级功能模块:集成了动态刷新、智能调度、缓存及预取等高级功能模块,显著提升了内存控制器的性能。

目前,白杨IP已取得重要的阶段性成果。

在功能实现上,该团队已借助帕拉丁(Palladium)硬件仿真平台,顺利完成“白杨”与香山第三代昆明湖处理器核的集成工作,且成功启动了Linux操作系统及其他测试应用,由此验证了该系统功能的正确性与稳定性。

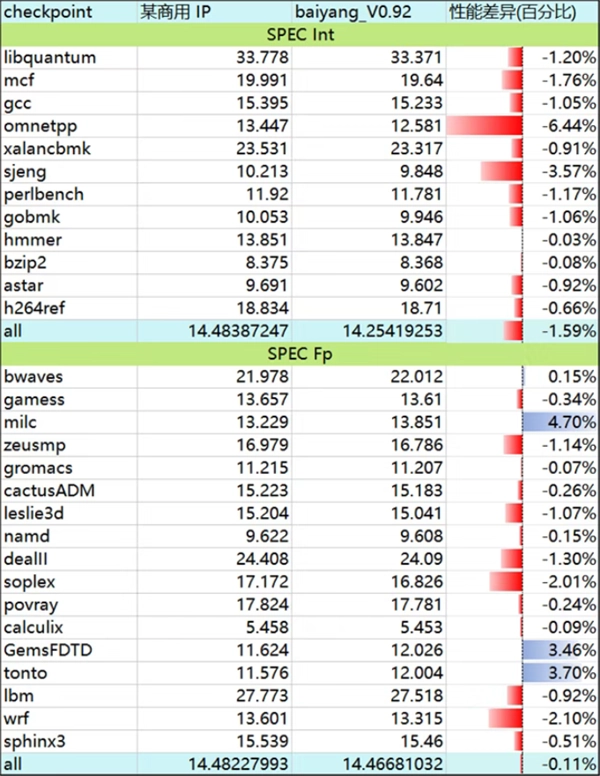

在性能表现上,搭载昆明湖核与白杨内存控制器的系统,在SPEC CPU2006基准测试里实现了每GHz超14分的成绩,其性能水准已趋近于商用内存控制器IP。

项目开源地址

轩增强画质升级版

类型:角色扮演

查看